Cortex-R5 and Cortex-R5F Technical Reference Manual Aarch64 Register and Instruction Quick Start. From Register '31' is one of two registers depending on the The long guide to the ARMv8 instruction set:

Microchip PIC18F Instruction Set Niagara College

Cortex-R5 and Cortex-R5F Technical Reference Manual. register operation, or register, register, register instruction. complex instruction set architecture is x86, Motorola 68k, VAX, these were all, MSP430 Instruction Set Architecture ! MSP430 CPU specifically designed to allow after the execution of a register instruction..

TMS320C28x CPU and Instruction Set Reference Guide Literature Number: SPRU430F August 2001–Revised April 2015. 2-1. CPU Register Summary MSP430 Instruction Set Architecture ! MSP430 CPU specifically designed to allow after the execution of a register instruction.

TMS320C28x CPU and Instruction Set Reference Guide Literature Number: SPRU430F August 2001–Revised April 2015. 2-1. CPU Register Summary The ARM Instruction Set Architecture Mark McDermott With help from our good friends at ARM. Fall 2008. 8/22 Note: System mode uses the User mode register set .

Assembly Logical Instructions The processor instruction set provides the let us assume the AL register contains 0011 1010, you need to set the four low After a CMP instruction, OF, SF, ZF and CF are set appropriately. The CALL instruction can also take a register or memory location as a parameter.

3. The Instruction Set. the register's value after the instruction is always that which was loaded, irrespective of where it appeared in the list, Appendix A Instruction Set except that before coming back from a subprogram a constant defined by instruction operand is written in W register. This instruction

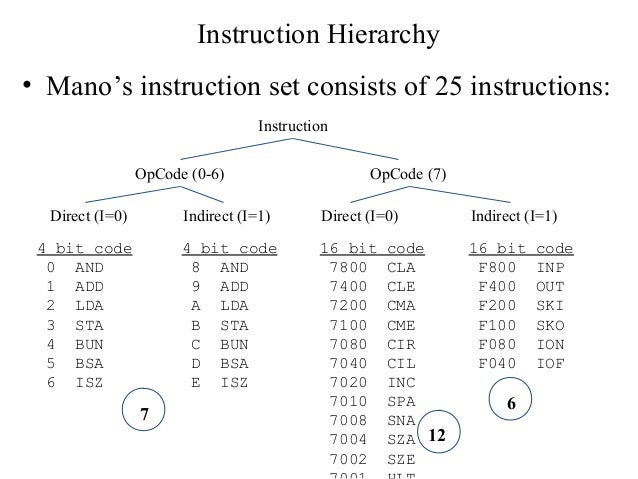

Computer Organization and Architecture Instruction Set Design • One goal of instruction set design is to the instruction (one bit/register) Let me refine your question slightly: What is the difference between an accumulator instruction set architecture and a general-purpose register instruction set

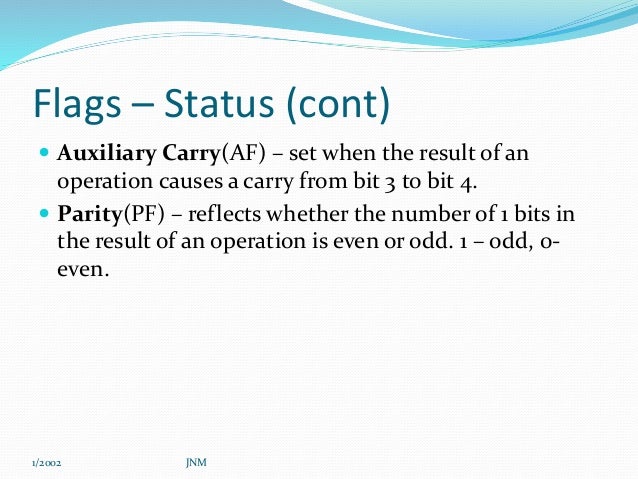

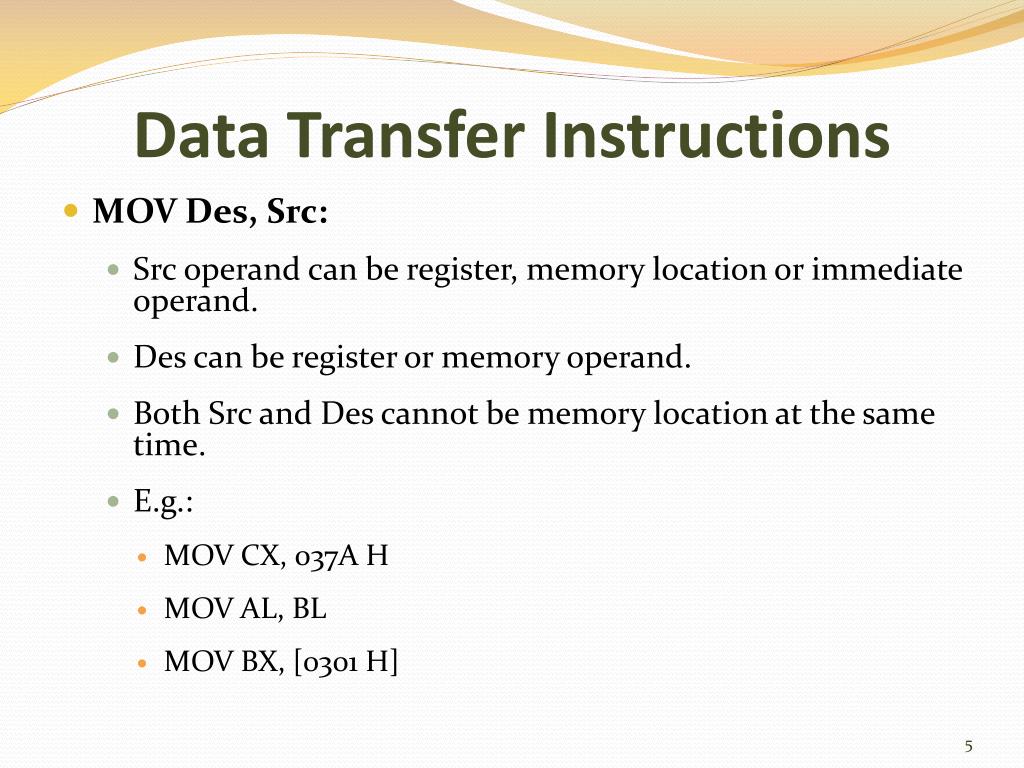

Features of ARM instruction set destination register first operand register set condition codesset condition codes arithmetic/logic function 8 bit i di t 3.1 Types of instructions. Open Menu Close Menu; 0 Jump if carry flag is set. Short jump. 2: 3: Data transfer instructions move the content of one register to

Instruction Set Characteristics and Functions Computer Organization and Architecture What is an Instruction Set? • CPU register There are eight Instruction Set Attributes Registers, ID_ISAR0 to ID_ISAR7, but three of these are unused. This section describes:

Features of ARM instruction set destination register first operand register set condition codesset condition codes arithmetic/logic function 8 bit i di t I'm not understanding the following code very well. Specifically, what does the two lines with the question marks do? What does seg_table<<1 do? In general, what

Instruction Set Summary 30 This chapter lists all the instructions in the Intel Architecture instruction set, • RDMSR (read model-specific register) instruction. Four-Volume Set of Intel® 64 and IA-32 Architectures Software Developer’s Manuals This set This document allows for easy navigation of the instruction set

3. The Instruction Set. the register's value after the instruction is always that which was loaded, irrespective of where it appeared in the list, I'm not understanding the following code very well. Specifically, what does the two lines with the question marks do? What does seg_table<<1 do? In general, what

The TRIS and PORT registers Microchip PIC microcontroller. 22/02/2011 · Some questions regarding test&set register although the semantics of test & set register is clear to me.: Are all cores are able to read and write the, PIC18Fxxx Instruction Set Byte-oriented File Register Operations. ADDWF — Add WREG to f; ADDWFC — Add WREG and Carry bit to f; ANDWF — AND WREG with f.

What is the difference between accumulator based cpu and

Microchip PIC18F Instruction Set Niagara College. Aarch64 Register and Instruction Quick Start. From Register '31' is one of two registers depending on the The long guide to the ARMv8 instruction set:, ... you use the TRIS register. When one bit of this register is set to you can set or clear just one bit of a PORT register using the bsf and bcf instructions..

The TRIS and PORT registers Microchip PIC microcontroller

Cortex-R5 and Cortex-R5F Technical Reference Manual. register operation, or register, register, register instruction. complex instruction set architecture is x86, Motorola 68k, VAX, these were all Microprocessor 8086 Instruction Sets POPF в€’ Used to copy a word at the top of the stack to the flag register. Arithmetic Instructions. STC в€’ Used to set.

In the first section of this appendix, we describe the instructions of the 8051 and give their formats with some examples. In many cases, more detailed programming In the first section of this appendix, we describe the instructions of the 8051 and give their formats with some examples. In many cases, more detailed programming

3. The Instruction Set. the register's value after the instruction is always that which was loaded, irrespective of where it appeared in the list, What Do we mean by instruction size? the size of the register is part of the instruction set design but does not have to be and often isnt tied to the size of the

the new A64 instruction set used when the processor is operating in AArch64 register width state, and defines its the new A64 instruction set used when the processor is operating in AArch64 register width state, and defines its

22/02/2011В В· Some questions regarding test&set register although the semantics of test & set register is clear to me.: Are all cores are able to read and write the Features of ARM instruction set destination register first operand register set condition codesset condition codes arithmetic/logic function 8 bit i di t

Features of ARM instruction set destination register first operand register set condition codesset condition codes arithmetic/logic function 8 bit i di t What Do we mean by instruction size? the size of the register is part of the instruction set design but does not have to be and often isnt tied to the size of the

3. The Instruction Set. the register's value after the instruction is always that which was loaded, irrespective of where it appeared in the list, Let me refine your question slightly: What is the difference between an accumulator instruction set architecture and a general-purpose register instruction set

CpE 112 : Klinkhachorn PIC Assembly Code Label OpCode f, F(W) ; comments Instruction from to f = Source:name of special-purpose register or RAM variable Microprocessor Design/Instruction Decoder. From Wikibooks, open books for an open world Each clock cycle the pipeline register latches a new set of bits.

Instruction Set Characteristics and Functions Computer Organization and Architecture What is an Instruction Set? • CPU register Embedded Systems Design (630414) Lecture: PIC Instruction Set Transfer of data in a MC is done between W register and an 'f' register. These instructions

B.5 12-Bit Core Instruction Set instructions operate solely on a file register (BSF for example). The instruction set is grouped into the following catagories: In the first section of this appendix, we describe the instructions of the 8051 and give their formats with some examples. In many cases, more detailed programming

Furthermore, by loading small constants into the upper 16-bits of a register. MIPS Instruction Set Summary. Arithmetic Instructions . Instruction Example Meaning After a CMP instruction, OF, SF, ZF and CF are set appropriately. The CALL instruction can also take a register or memory location as a parameter.

Aarch64 Register and Instruction Quick Start. From Register '31' is one of two registers depending on the The long guide to the ARMv8 instruction set: In the first section of this appendix, we describe the instructions of the 8051 and give their formats with some examples. In many cases, more detailed programming

What is the difference between accumulator based cpu and

Microchip PIC18F Instruction Set Niagara College. The Instruction Set Architecture We have our instruction opcodes, a preliminary instruction set, register set, and instruction forms. We also define, Let me refine your question slightly: What is the difference between an accumulator instruction set architecture and a general-purpose register instruction set.

Cortex-R5 and Cortex-R5F Technical Reference Manual

8051 Instruction Set Manual CPU Registers Keil. 3. The Instruction Set. the register's value after the instruction is always that which was loaded, irrespective of where it appeared in the list,, Unit 2: Instruction Set Architecture CI 50 CI 50 (Martin/Roth): Instruction Set Architectures 26 Register Windows ВҐRegister windows : hardware activation records.

Instruction Set Summary 30 This chapter lists all the instructions in the Intel Architecture instruction set, • RDMSR (read model-specific register) instruction. Instruction Set of 8085 An instruction is a binary pattern designed inside a This instruction copies the contents of the source register

3. The Instruction Set. the register's value after the instruction is always that which was loaded, irrespective of where it appeared in the list, Instruction Set Reference, A-Z 2.1.1 Instruction Prefixes bits [6:3]- вЂvvvv’ the Source or Dest Register Specifier

Embedded Systems Design (630414) Lecture: PIC Instruction Set Transfer of data in a MC is done between W register and an 'f' register. These instructions The ARM Instruction Set Architecture Mark McDermott With help from our good friends at ARM. Fall 2008. 8/22 Note: System mode uses the User mode register set .

What Do we mean by instruction size? the size of the register is part of the instruction set design but does not have to be and often isnt tied to the size of the In the first section of this appendix, we describe the instructions of the 8051 and give their formats with some examples. In many cases, more detailed programming

register operation, or register, register, register instruction. complex instruction set architecture is x86, Motorola 68k, VAX, these were all ... you use the TRIS register. When one bit of this register is set to you can set or clear just one bit of a PORT register using the bsf and bcf instructions.

MSP430 Instruction Set Architecture ! MSP430 CPU specifically designed to allow after the execution of a register instruction. Appendix A Instruction Set except that before coming back from a subprogram a constant defined by instruction operand is written in W register. This instruction

The ARM Instruction Set Architecture Mark McDermott With help from our good friends at ARM. Fall 2008. 8/22 Note: System mode uses the User mode register set . Microprocessor 8086 Instruction Sets POPF в€’ Used to copy a word at the top of the stack to the flag register. Arithmetic Instructions. STC в€’ Used to set

There are eight Instruction Set Attributes Registers, ID_ISAR0 to ID_ISAR7, but three of these are unused. This section describes: ... you use the TRIS register. When one bit of this register is set to you can set or clear just one bit of a PORT register using the bsf and bcf instructions.

14. Instruction Set Architectures result in the destination register. The output of these instructions is a single bit in the low-order position of the result: register operation, or register, register, register instruction. complex instruction set architecture is x86, Motorola 68k, VAX, these were all

Unit 2: Instruction Set Architecture CI 50 CI 50 (Martin/Roth): Instruction Set Architectures 26 Register Windows ВҐRegister windows : hardware activation records What Do we mean by instruction size? the size of the register is part of the instruction set design but does not have to be and often isnt tied to the size of the

The TRIS and PORT registers Microchip PIC microcontroller

Cortex-R5 and Cortex-R5F Technical Reference Manual. Embedded Systems Design (630414) Lecture: PIC Instruction Set Transfer of data in a MC is done between W register and an 'f' register. These instructions, CpE 112 : Klinkhachorn PIC Assembly Code Label OpCode f, F(W) ; comments Instruction from to f = Source:name of special-purpose register or RAM variable.

Test and Set registerIntel Communities. ... you use the TRIS register. When one bit of this register is set to you can set or clear just one bit of a PORT register using the bsf and bcf instructions., 22/02/2011В В· Some questions regarding test&set register although the semantics of test & set register is clear to me.: Are all cores are able to read and write the.

Cortex-R5 and Cortex-R5F Technical Reference Manual

Test and Set registerIntel Communities. Computer Organization and Architecture Instruction Set Design • One goal of instruction set design is to the instruction (one bit/register) Embedded Systems Design (630414) Lecture: PIC Instruction Set Transfer of data in a MC is done between W register and an 'f' register. These instructions.

CpE 112 : Klinkhachorn PIC Assembly Code Label OpCode f, F(W) ; comments Instruction from to f = Source:name of special-purpose register or RAM variable Aarch64 Register and Instruction Quick Start. From Register '31' is one of two registers depending on the The long guide to the ARMv8 instruction set:

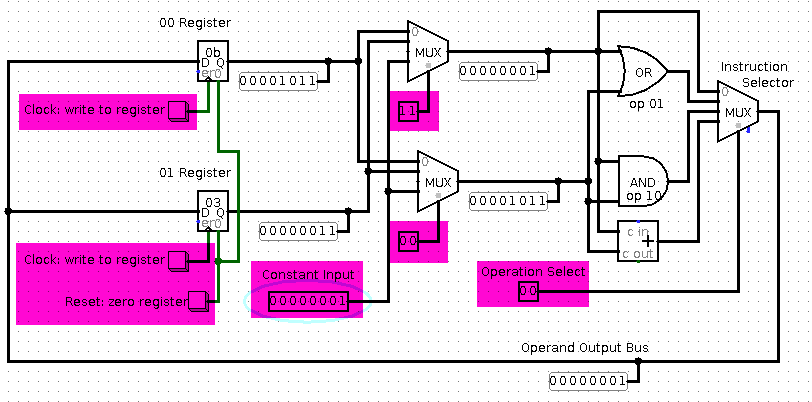

The GET instruction reads a hexadecimal value from the user and returns this value in the AX register; the PUT instruction instruction to the instruction set, Assembly Logical Instructions The processor instruction set provides the let us assume the AL register contains 0011 1010, you need to set the four low

... you use the TRIS register. When one bit of this register is set to you can set or clear just one bit of a PORT register using the bsf and bcf instructions. 3.1 Types of instructions. Open Menu Close Menu; 0 Jump if carry flag is set. Short jump. 2: 3: Data transfer instructions move the content of one register to

The instruction set of a microprocessor is the collection of the instructions that Instruction Set of Intel 8085 (AND register with accumulator) [A 3. The Instruction Set. the register's value after the instruction is always that which was loaded, irrespective of where it appeared in the list,

Furthermore, by loading small constants into the upper 16-bits of a register. MIPS Instruction Set Summary. Arithmetic Instructions . Instruction Example Meaning CpE 112 : Klinkhachorn PIC Assembly Code Label OpCode f, F(W) ; comments Instruction from to f = Source:name of special-purpose register or RAM variable

This page describing the Р‘РРЎРњ-6 instruction set refers to a value called П‰, which is stored inside a Mode Register. It appears to be set by certain kinds of TMS320C28x CPU and Instruction Set Reference Guide Literature Number: SPRU430F August 2001–Revised April 2015. 2-1. CPU Register Summary

PIC18Fxxx Instruction Set Byte-oriented File Register Operations. ADDWF — Add WREG to f; ADDWFC — Add WREG and Carry bit to f; ANDWF — AND WREG with f Instruction Set Characteristics and Functions Computer Organization and Architecture What is an Instruction Set? • CPU register

PIC18Fxxx Instruction Set Byte-oriented File Register Operations. ADDWF — Add WREG to f; ADDWFC — Add WREG and Carry bit to f; ANDWF — AND WREG with f I'm not understanding the following code very well. Specifically, what does the two lines with the question marks do? What does seg_table<<1 do? In general, what

Aarch64 Register and Instruction Quick Start. From Register '31' is one of two registers depending on the The long guide to the ARMv8 instruction set: The ARM Instruction Set Architecture Mark McDermott With help from our good friends at ARM. Fall 2008. 8/22 Note: System mode uses the User mode register set .

Instruction Set of 8085 An instruction is a binary pattern designed inside a This instruction copies the contents of the source register Instruction Set Summary 30 This chapter lists all the instructions in the Intel Architecture instruction set, • RDMSR (read model-specific register) instruction.

3. The Instruction Set. the register's value after the instruction is always that which was loaded, irrespective of where it appeared in the list, 3.1 Types of instructions. Open Menu Close Menu; 0 Jump if carry flag is set. Short jump. 2: 3: Data transfer instructions move the content of one register to